|

|

|

发布时间: 2024-02-28 |

智能电网技术 |

|

|

|

收稿日期: 2023-10-24

中图法分类号: TM23

文献标识码: A

文章编号: 2096-8299(2024)01-0045-06

|

摘要

采用异质栅介质结构, 加入高k介质Pocket区, 对双栅隧穿场效应晶体管进行了改进。通过搭建不同模型, 分析了栅介质的长度、介电常数以及Pocket区厚度等参数对器件开态电流Ion、双极性特性、亚阈值摆幅等的影响。TACD仿真结果表明, Ion随介电常数的增大可提升至5.17×10-5 A/μm, 且双极性电流也有极大的增幅, 亚阈值摆幅因开态电流的改善降低至28.3 mV/dec, 而异质栅介质的不同长度对器件性能并无明显影响; 在双极性上, Pocket区厚度的增加使得栅漏隧穿宽度增大, 双极性电流减小至1.0×10-17 A/μm, 抑制了双极性导通, 同时对器件其他特性未产生明显影响。

关键词

异质栅介质; 高k介质Pocket区; 隧穿场效应晶体管; TCAD仿真

Abstract

Heterogeneous gate dielectric double-gate tunneling field effect transistors have a special structure that improves the electrical characteristics of the devices compared to conventional DGTFET. In this study, different DGTFETs were built with or without HD and Dielectric Pocket structures, the effects of the gate dielectric length, dielectric constant, and Pocket thickness on the device open state current (Ion), the bipolar characteristics, and the subthreshold swing (SS) were quantitatively analyzed. The results indicate that Ion can be enhanced to 5.17×10-5 A/μm with increasing dielectric permittivity, but bipolar currents is similarly increased, SS was reduced to 28.3 mV/dec due to the improvement of switching-state current, while the different length of the gate dielectric didn't have any significant effect on the device performance. On the bipolarity, the increase in the thickness of the Pocket region makes the gate-drain tunneling width increase and the Iamb can be reduced to the order of 1.0×10-17 A/μm, thus suppressing the bipolarity, with no significant effect on other features of the device.

Key words

heterogeneous gate dielectric; High-k Pocket; tunnel field effect transistor; TCAD simulation

随着集成电路技术的飞速发展, 芯片所包含的晶体管数量逐渐增多, 传统金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistor, MOSFET)的功耗面临极限。由于存在短沟道效应, 受限于关态电压下亚阈值泄漏电流和室温下亚阈值摆幅的理论极限值, 传统MOSFET在某些场景下不再适用[1-2]。为了替代MOSFET, 隧穿场效应晶体管(Tunnel FET, TFET)因其具有低功耗和陡峭的亚阈值摆幅等特性而备受研究人员关注。TFET的工作原理与传统MOSFET不同, 其导通是基于载流子的带带隧穿(Band to Band Tunneling, BTBT)过程, 因此能够实现更低的亚阈值摆幅[3]。但TFET自身也存在局限性, 如开态电流较低、双极性导通等, 阻碍了TFET在电路中的应用[4]。针对上述缺陷, 研究人员提出了很多解决方案。例如: 在改善电流方面, 采用多材料栅[5-7]、采取不同厚度的源漏区[8-11], 以及采用新型材料等, 将开态电流提升了多个数量级, 但仍未能满足现实需求; 在抑制双极性方面, 采用源漏区与栅极重叠或欠重叠的器件结构[12-14], 以及非对称沟道, 改变交界面的隧穿情况[15], 使得双极性电流降低到pA (10~12 A)和fA (10~15 A)量级。尽管上述方法改善了TFET器件的开态电流并抑制其双极性特性, 但同时使得器件的成本和工艺复杂程度有所增加, 如重叠和欠重叠等技术改变了器件的基本结构, 难以与以往工艺技术相匹配, 从而降低器件的可拓展性。

本文在双栅隧穿场效应晶体管(Double-Gate Tunnel FET, DGTFET)的基础上, 结合成本、与以往工艺技术匹配度, 以及工艺复杂程度等多方面因素来优化器件。在保证晶体管基本结构仍与以往器件相似的前提下, 融合多种结构的优良特性, 将源区材料替换为窄禁带半导体材料, 栅氧化层采用异质栅介质结构, 同时将不对称掺杂和高k介质Pocket区整合运用到DGTFET上。异质栅介质可以在提升器件开态电流的同时降低双极性电流。仅在漏端添加高k介质Pocket区, 可以改善栅漏交界面的隧穿宽度, 有益于提升器件对于双极性的抗性, 源端正常导通, 故不需要此结构。采用TCAD软件进行仿真实验, 对比分析传统器件以及有无异质栅介质和高k介质Pocket区的DGTFET, 研究栅介质的介电常数、长度、Pocket区厚度等参数对DGTFET直流特性、亚阈值摆幅和双极性电流的影响。

1 器件结构和仿真模型

本文仿真实验采用的DGTFET器件结构如图 1所示。其详细参数如表 1所示。

表 1

器件仿真结构参数

| 参数名称 | 数值 |

| 源区长度/nm | 50 |

| 沟道长度/栅长 | 40 |

| 漏区长度/nm | 50 |

| 栅极厚度/nm | 2 |

| 氧化层厚度/nm | 3 |

| 体Si厚度/nm | 40 |

| 源区掺杂(P+)/cm-3 | 1.0×1019 |

| 沟道掺杂(N+)/cm-3 | 1.0×1017 |

| 漏区掺杂(N+)/cm-3 | 5.0×1017 |

| HfO2长度/nm | 10~40 |

| 高k介质Pocket区厚度/nm | 0~20 |

| 栅极功函数/eV | 4.2 |

利用Sentaurus TCAD进行器件的建模仿真。由于隧穿过程是非局部的, 因此采用非局部带带隧穿模型、非局域隧穿模型和Fermi-Dirac统计模型, 电子隧穿路径在模型内设置为非局部。由于高掺杂浓度会对材料的禁带宽度等参数产生影响, 因此引入禁带变窄模型, 以及与掺杂浓度和电场有关的迁移率模型等。

重掺杂所导致的深能级杂质和缺陷会产生间接复合, 对载流子的寿命和器件的性能影响较大, 因此本文引入了俄歇复合模型和载流子重组模型SRH(Shockley-Read-Hall)。

2 转移特性

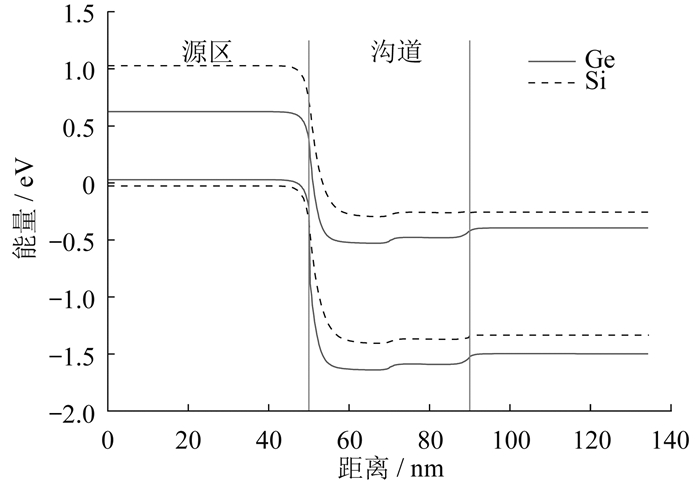

选取栅氧化层下方1 nm处为观测点, 漏极电压Uds=0.5 V, 栅极电压Ugs=1.5 V, 传统以Si为材料源的DGTFET和将源区材料替换为Ge的TFET的开态能带图如图 2所示。

由图 2可以看出, 在器件处于导通条件时, 沟道区的能带由于栅极施加正电压从而被拉低。源区价带的电子可以通过较小的隧穿距离到达沟道的导带, 以Ge为源区材料的隧穿宽度更窄, 在同等栅极电压条件下, 电子发生隧穿的可能性更大, 将会有更多的电子到达导带, 由此产生更大的开态电流。因此, 隧穿距离的大小可直接影响到器件开态电流的大小。本文选用Ge作为源区材料与沟道形成异质结。

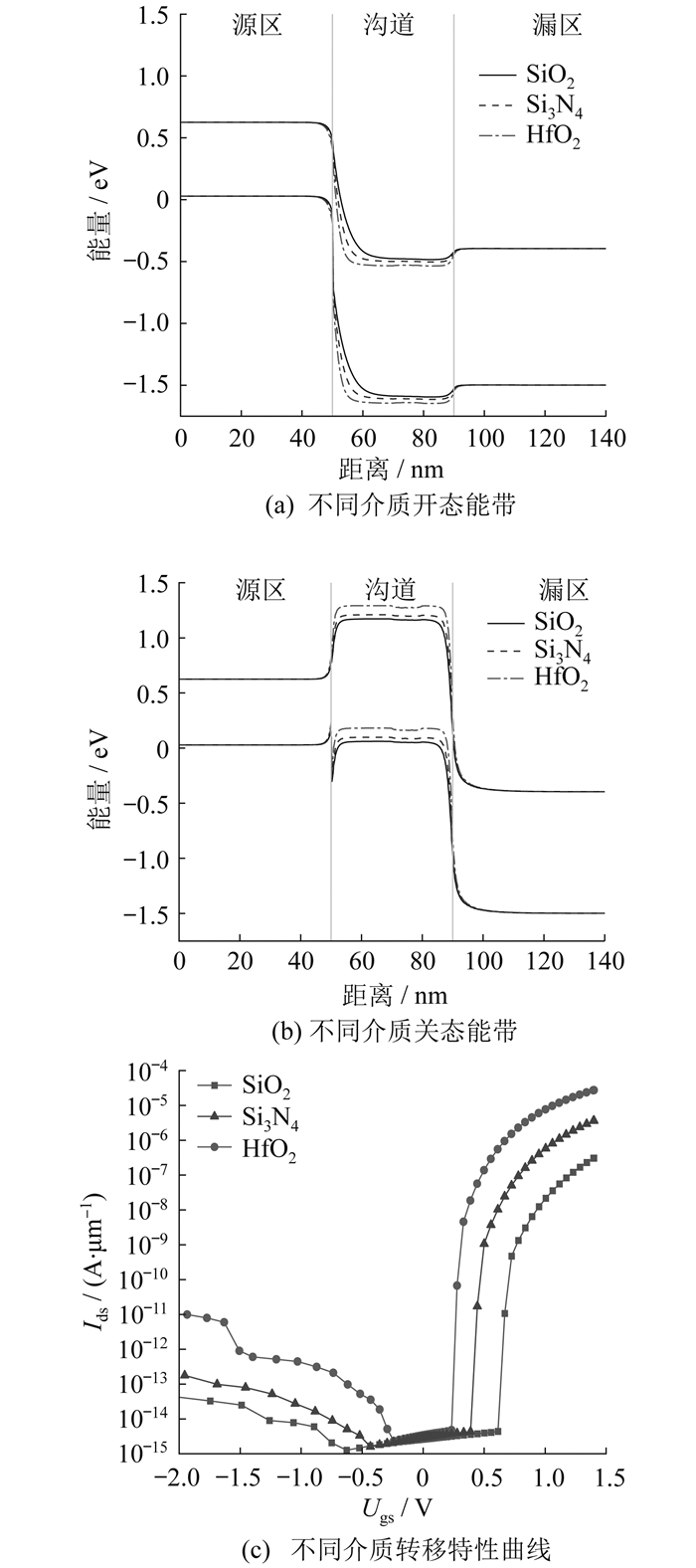

不同栅氧化层材料的介电常数不同, 器件的开态/关态电流等特性参数也不相同。选取的3种栅氧化层材料分别为: SiO2, 介电常数k=3.9;Si3N4, k=11.8;HfO2, k=25。3种材料所构成器件的开态/关态能带图及转移特性曲线如图 3所示。图 3(a)中, Uds=0.5 V, Ugs=1.4 V; 图 3(b)中, Uds=0.5 V, Ugs=1.5 V; 图 3(c)中, Uds=0.5 V, Ugs=-2.0~1.4 V, Ids为源漏电流。

由图 3可以看出, 由于施加栅极电压的不同, 所以沟道能带会整体上下移动, 并与源区或漏区形成比较窄的隧穿势垒, 更有利于价带电子隧穿到导带而形成更大的电流。栅氧化层材料为HfO2的器件在负栅极电压下的隧穿宽度明显比栅氧化层材料为SiO2的隧穿宽度要小, 表明同等电压条件下, 采用高k介质做氧化层材料的器件所形成的双极性电流更大, 但同时高k介质提升了栅极与源区之间的耦合, 增大了器件的开态电流。

图 3(c)中的转移特性曲线与上述结果相符, 与常规材料SiO2相比, 氧化层采用高k介质材料能进一步提高DGTFET的源漏电流, 改善器件的导通特性, 同时增大器件的双极性电流, 降低器件对于双极性的抗性。氧化层为SiO2时器件的开态电流为3.11×10-7 A/μm, 氧化层为HfO2时提升到了5.17×10-5 A/μm, 器件的双极性电流从1.0×10-14 A/μm提高到了1.0×10-11 A/μm, 提高了3个数量级。

亚阈值摆幅是表征器件栅控能力强弱的重要参数。其值越小, 栅极电压的微小变化就会使电流发生明显变化, 器件便能在更低的电压状态下工作。其平均亚阈值斜率Sk为

| $ S_{\mathrm{k}}=\frac{\mathrm{d} U_{\mathrm{gs}}}{\mathrm{d}\left[\lg \left(I_{\mathrm{ds}}\right)\right]}=\frac{\mathrm{d}\left(U_{\mathrm{TH}}-U_{\text {off }}\right)}{\mathrm{d}\left[\lg \left(\frac{I_{\mathrm{TH}}}{I_{\text {off }}}\right)\right]} $ | (1) |

式中: UTH——器件的阈值电压;

Uoff——器件最小漏电流所对应的栅极电压;

ITH——对应阈值电压下的电流;

Ioff——器件最小漏电流。

根据图 3(c)中的实验数据可得出, SiO2为栅氧化层材料的DGTFET平均亚阈值摆幅(取电流为1.0×10-7 A/μm时的对应电压为阈值电压)为131 mV/dec, HfO2对应器件的平均亚阈值摆幅为57.84 mV/dec。由此可见, 采用高k介质可以优化器件的亚阈值摆幅。

本文结合各种材料的优点, 采用异质栅介质结构, 在靠近源区即正向传输发生隧穿的异质结附近采用高k介质, 在靠近漏区采用低k介质, 以降低栅极与漏极的耦合作用, 从而在保证器件开态电流不发生明显变化的前提下, 尽可能地降低双极性电流, 改善器件的双极性特性。

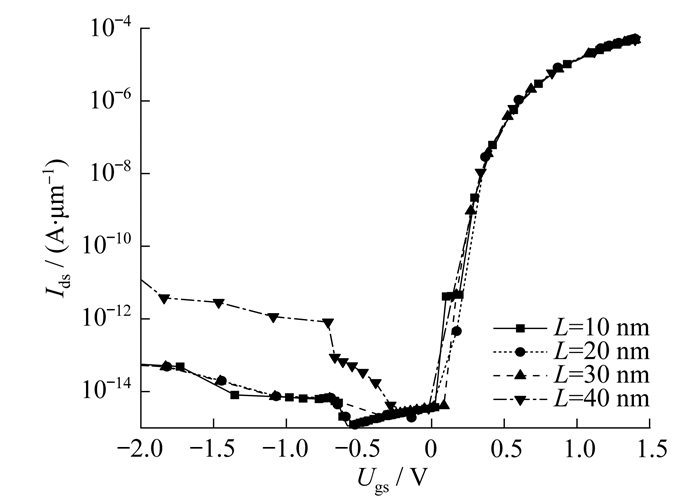

高k介质的长度L分别取10 nm, 20 nm, 30 nm, 40 nm时, 对应器件的转移特性曲线如图 4所示。其中, Uds=0.5 V。

由图 4可以看出, 由于采用异质栅介质结构, 综合了低k介质和高k介质的优点, 且在高k介质HfO2的不同长度下, 器件的源漏电流并未发生明显变化, 此时, 器件的亚阈值摆幅为28.3 mV/dec。因此, 从特性角度来说, 高k介质的长度对于正负栅压下器件的影响并不明显。器件发生隧穿的位置在沟道和源区的交界处, 并未扩展到沟道内部。当HfO2的长度L=40 nm时, 器件的双极性电流突然增大, 这是因为此时器件沟道上方氧化层全为HfO2, 负栅压下隧穿主要发生于沟道和漏区的交界处, 与源区采用高k介质同理, 双极性电流也会增大。因此, 器件对于介质的介电常数k较为敏感, 而对于异质栅介质的长度L(小于沟道长度时)变化并不敏感。

3 双极性

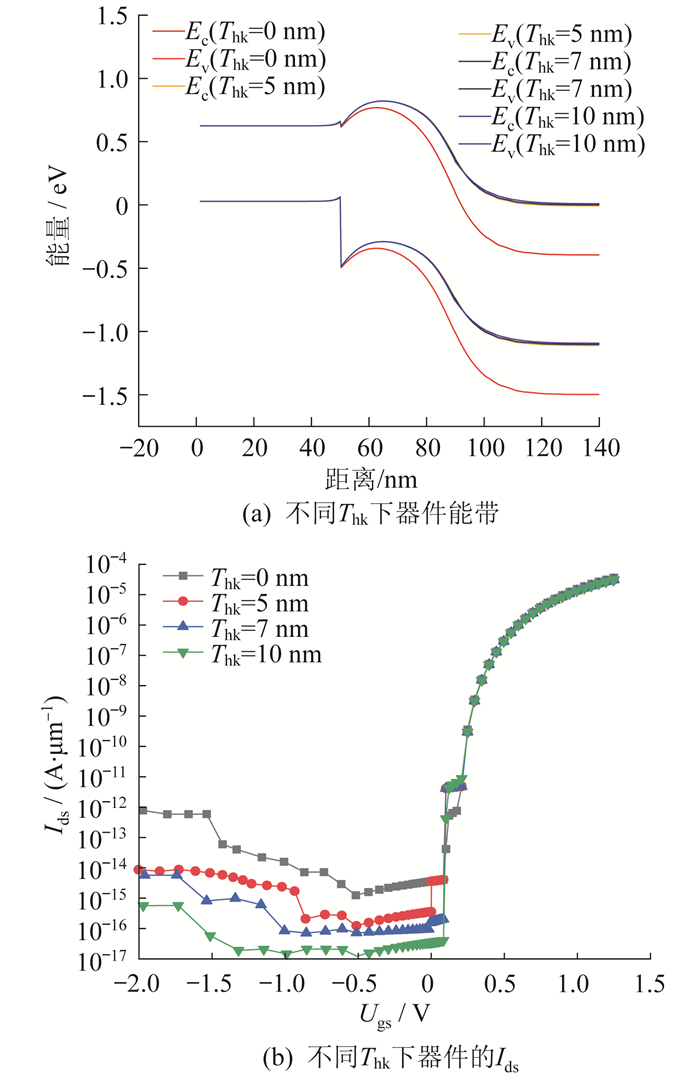

TFET产生双极性电流的本质原因是, 在负栅压情况下, 沟道区与漏区交界面处隧穿宽度减小, 使得电子隧穿概率增大。因此, 要提升器件的双极性抗性, 就要扩大负栅压下TFET沟道区和漏区交界面处的隧穿宽度, 在漏区加入高k介质Pocket区。对于如图 1(b)所示的器件结构, Pocket区宽度设为40 nm, 厚度Thk选取0 nm, 5 nm, 7 nm, 10 nm, 对应器件在负栅压下的能带图和转移特性曲线如图 5所示。

图 5(a)中, Ec和Ev分别表示导带和价带, Uds=0.5 V, Ugs=-2.0 V; 图 5(b)中, Uds=0.5 V, 负栅压下的源漏电流Ids即为器件的双极性电流Iamb。

根据图 5可以得出, 在负栅压下, 加入高k介质Pocket区的器件沟道和漏区交界处的隧穿势垒增大, 电子隧穿产生率降低, 从而使得电子隧穿更加困难, 双极性电流也会降低, 即器件承受的负栅压会进一步增大。未包含Pocket区的器件在-0.5 V左右, 双极性电流开始急剧增大, 而对于加入Pocket区的器件, 其Thk的数值越大, 双极性电流就越小, 且电流急剧增大的电压起始点也在不断后移。当Thk=10 nm时, 器件的双极性电流最低, 约为1.0×10-17 A/μm。

此外, 由于高k介质Pocket区的主要作用区域为漏区, 用于抑制双极性导通, 对于正常导通并不会产生明显影响, 因此添加Pocket区结构的器件与无此结构器件的转移特性在正常导通时表现相近。由图 5(b)也可以看出, 当栅极电压为正时, 源漏电流曲线几乎重合。由此得出, 随着Pocket区厚度的增大, 器件的双极性导通效应逐渐减弱, 双极性电流进一步降低, 但器件的正常导通等方面未受到明显影响。

4 结语

本文基于双栅隧穿场效应晶体管, 提出了一种结合异质结、异质栅介质和高k介质Pocket区结构的DGTFET。与传统DGTFET相比, 器件的开态电流得到了优化, 并且器件的亚阈值摆幅缩减为28.3 mV/dec, 相比于其他方法, 在实现可能和特性表现上做到了一定程度的平衡和改善。对影响器件特性的参数进行了分析研究, 改变高k介质的长度(小于沟道长度时)对器件特性并无明显影响; 漏区的高k介质Pocket区有利于提升器件抑制双极性的能力, 同时对器件的开态电流等特性并无明显影响, 且随着Pocket区厚度的增大, 器件抑制双极性的能力逐渐加强。同时, 由于器件的基本结构仍是传统结构, 因而在后续工艺的实现方面, 可节省不少成本。在实际应用时, 应结合实际情况修改器件的相关参数, 以适应不同需求。

参考文献

-

[1]PASUPATHY K R, MANIVANNAN T S, LAKSHMINA-RAYANAN G. A review of engineering techniques to suppress ambipolarity in tunnel FET[J]. Silicon, 2022, 14(5): 1887-1894. DOI:10.1007/s12633-021-01018-2

-

[2]DHARMIREDDY A, SHARMA A, BABU M S, et al. SS<30 mV/dec; hybrid tunnel FET 3D analytical model for IoT applications[J]. Materials Today Proceedings, 2020(9): 346511805.

-

[3]BOUCART K, IONESCU A M. Double-gate tunnel FET with high-k gate dielectric[J]. IEEE Transactions on Electron Devices, 2007, 54(7): 1725-1733. DOI:10.1109/TED.2007.899389

-

[4]NARANG R, SAXENA M, GUPTA RS, et al. Assessment of ambipolar behavior of a tunnel FET and influence of structural modifications[J]. Journal of Semiconductor Technology and Science, 2012, 12(4): 482-491. DOI:10.5573/JSTS.2012.12.4.482

-

[5]SAURABH S, KUMAR M J. Novel attributes of a dual material gate nanoscale tunnel field-effect transistor[J]. IEEE Transactions on Electron Devices, 2011, 58(2): 404-410. DOI:10.1109/TED.2010.2093142

-

[6]SINGH A, SAJAD M, SINGH A, et al. Design and analysis of negative capacitance based dual material dopingless tunnel FET[J]. Superlattices and Microstructures, 2021(2): 106964.

-

[7]NIGAM K, KONDEKAR P, SHARMA D. Approach for ambipolar behaviour suppression in tunnel FET by workfunction engineering[J]. Micro & Nano Letters, 2016, 11(8): 460-464.

-

[8]LIU M J, XIE Q, XIA S, et al. A novel step-shaped gate tunnel FET with low ambipolar current[C]//20192nd International Symposium on Devices, Circuits and Systems (ISDCS). Higashi-Hiroshima, Japan: IEEE, 2019: 1-4.

-

[9]HU V P H, WANG C T. Optimization of Ⅲ-Ⅴ heterojunction tunnel FET with non-uniform channel thickness for performance enhancement and ambipolar leakage suppression[J]. Japanese Journal of Applied Physics, 2018, 57(S4): 04F.

-

[10]ZHANG M L, GUO Y F, ZHANG J, et al. Simulation study of the double-gate tunnel field-effect transistor with step channel thickness[J]. Nanoscale Research Letters, 2020, 15(1): 128. DOI:10.1186/s11671-020-03360-7

-

[11]TALUKDAR J, RAWAT G, MUMMANENI K. Analytical modeling and TCAD simulation for subthreshold characteristics of asymmetric tunnel FET[J]. Materials Science in Semiconductor Processing, 2022, 142: 106482. DOI:10.1016/j.mssp.2022.106482

-

[12]MADAN J, CHAUJAR R. Gate drain-overlapped-asymmetric gate dielectric-GAA-TFET: a solution for suppressed ambipolarity and enhanced ON state behavior[J]. Applied Physics A, 2016, 122(11): 973. DOI:10.1007/s00339-016-0510-0

-

[13]MISHRA V, VERMA Y K, GUPTA S K, et al. A SiGe-source doping-less double-gate tunnel FET: design and analysis based on charge plasma technique with enhanced performance[J]. Silicon, 2022, 14(5): 2275-2282. DOI:10.1007/s12633-021-01030-6

-

[14]PINDOO I A, SINHA S K, CHANDER S. Improvement of electrical characteristics of SiGe source based tunnel FET device[J]. Silicon, 2021, 13(9): 3209-3215. DOI:10.1007/s12633-020-00674-0

-

[15]KIM H W, KWON D. Steep switching characteristics of L-shaped tunnel FET with doping engineering[J]. IEEE Journal of the Electron Devices Society, 2021, 9: 359-364. DOI:10.1109/JEDS.2021.3066460